# Logic Set

# Experimental kit by Brick'R'knowledge Experimentierkasten von Brick'R'knowledge

www.brickrknowledge.com

# Imprint

Brick'R'knowledge Logic Set Manual Rev. 1.0 Date: 07.04.2017

ALLNET<sup>®</sup> and Brick'R'knowledge<sup>®</sup> are registered trademarks of ALLNET<sup>®</sup> GmbH Computersysteme.

ALLNET<sup>®</sup> GmbH Computersysteme Brick'R'knowledge Maistraße 2 D-82110 Germering

© Copyright 2017 ALLNET GmbH Computersysteme. All rights reserved.

All of the information that are included in this manual has been put together with great care and to the best of our knowledge. Even though it errors can occur. We are always thankful for any feedback about possible mistakes. Please send your feedback to: info@brickrknowledge.de.

# Contents

| 1. | . Safety instructions                                             | 5  |

|----|-------------------------------------------------------------------|----|

| 2  | . Basics of the Brick'R'knowledge system                          | 6  |

|    | 2.1 The ground brick                                              |    |

|    | 2.2 The power supply                                              | 6  |

|    | 2.3 The connectors                                                | 7  |

| 3. | . The Logic Set                                                   | 8  |

|    | 3.1 Bricks of the Logic Set                                       |    |

| Δ  | . Basics of the digital circuit technology                        |    |

| 4. | 4.1 What does digital actually mean?                              |    |

|    | 4.2 Logical functions                                             |    |

|    | 4.3 Comparison of numberal systems                                |    |

|    | 4.4 Logic levels                                                  |    |

|    | 4.4.1 Voltage ranges                                              |    |

|    | 4.4.2 Logical states                                              |    |

|    | 4.5 Combinatorial circuits                                        |    |

|    | 4.6 Sequential circuit                                            | 21 |

|    | 4.7 Glitches                                                      | 22 |

|    | 4.8 Programmable logic blocks                                     | 23 |

|    | 4.8.1 Programmable array logic (PAL) or generic array logic (GAL) | 23 |

|    | 4.8.2 Complex programmable logic device                           | 23 |

|    | 4.8.3 Field programmable gate array                               | 23 |

|    | 4.8.3.1 Basic structure of a FPGAs                                |    |

|    | 4.8.3.2 Configurable logic blocks (CLBs)                          |    |

|    | 4.8.3.3 On / off blocks (IOBs)                                    | 25 |

| 5. | . Circuit examples                                                | 26 |

|    | 5.1 Basic Circuits                                                | 26 |

|    | 5.1.1 Inverter                                                    | 26 |

|    | 5.1.2 AND gate                                                    |    |

|    | 5.1.3 OR gate                                                     |    |

|    | 5.1.4 NAND gate                                                   |    |

|    | 5.1.5 NOR gate                                                    |    |

|    | 5.1.6 XOR gate                                                    | 31 |

|    | 5.1.7 XNOR gate                                                   |    |

|    | 5.2 Antibeat device circuit                                       |    |

|    | 5.3 Digital counter                                               |    |

|    | 5.3.1       1-bit half-adder         5.3.2       1-bit full-adder |    |

|    | 5.3.2 4-bit full-adder                                            |    |

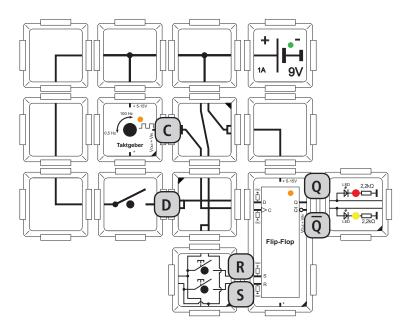

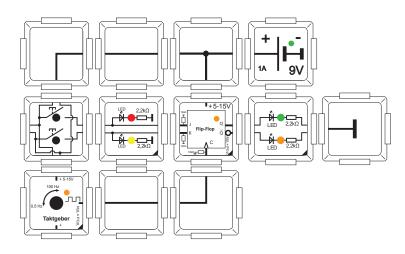

|    | 5.4 Flip-flop / bistable circuit                                  |    |

|    | 5.4.1 Types of flip-flops                                         |    |

|    | 5.4.1.1 Non-clocked flip-flops                                    |    |

|    | 5.4.1.2 State-controlled flip-flops                               |    |

|    | 5.4.1.3 One edge-controlled flip-flop                             |    |

|    | 5.4.1.4 Two edge controlled flip-flop                             |    |

|    | 5.4.2 RS flip-flop                                                |    |

|    | 5.4.3 D flip-flop                                                 |    |

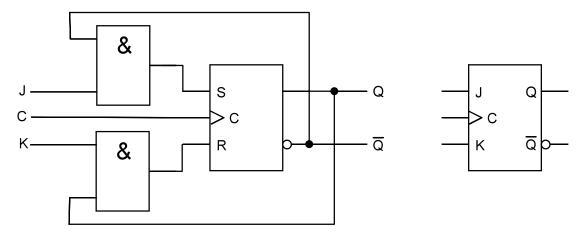

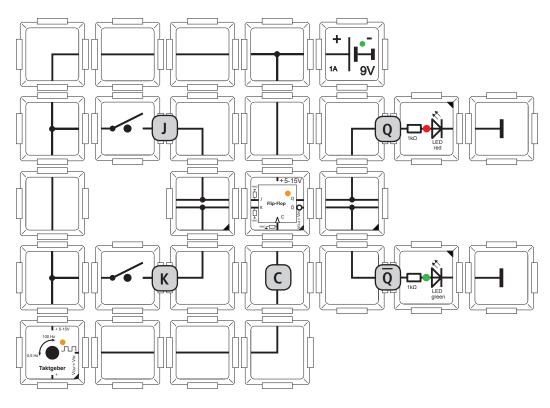

|    | 5.4.4 JK flip-flop                                                | 42 |

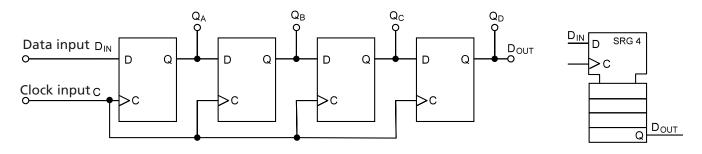

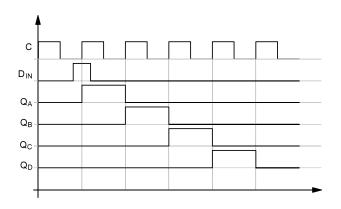

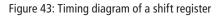

|    | 5.5 Shift register                                                | 44 |

|    | 5.5.1 Shift register with serial charging                         | 44 |

|    |                                                                   |    |

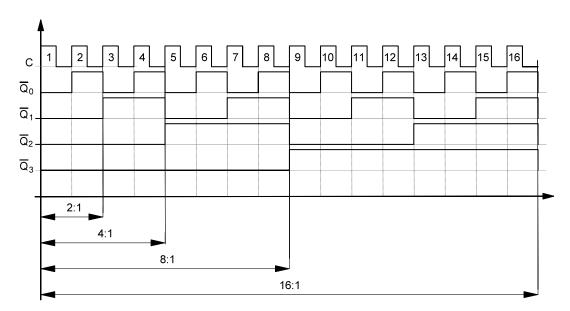

|    | 5.6 Counters                               | 45 |

|----|--------------------------------------------|----|

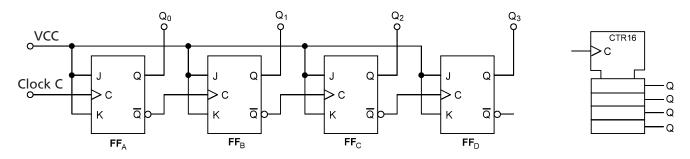

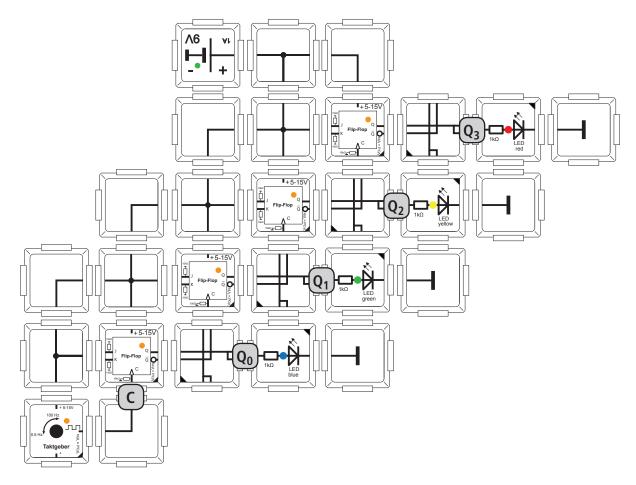

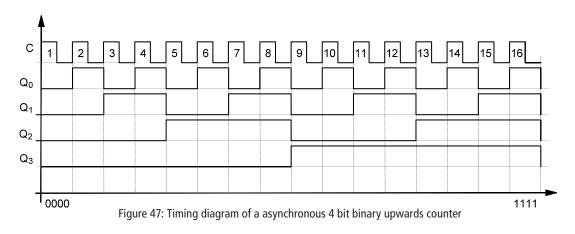

|    | 5.6.1 Asynchronous 4 bit binary counter    | 46 |

|    | 5.6.1.1 Asynchronous upwards counter       | 47 |

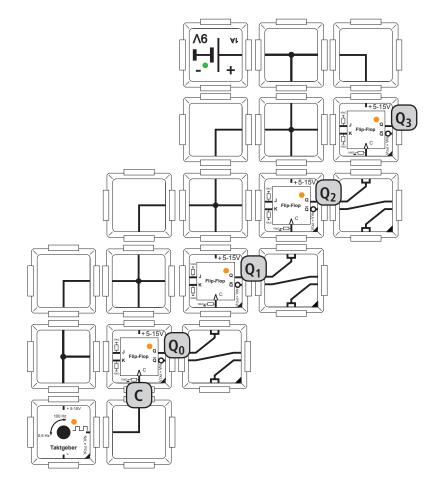

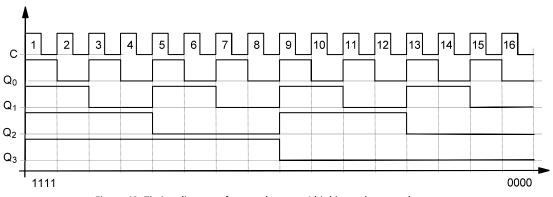

|    | 5.6.1.2 Asynchronous downwards counter     | 48 |

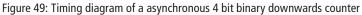

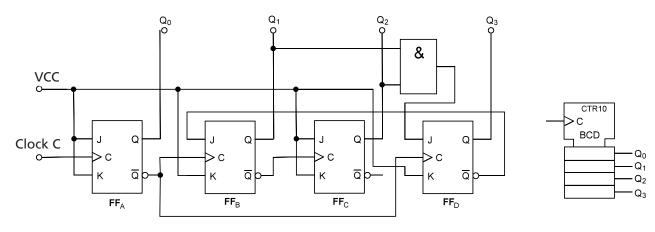

|    | 5.6.2 Asynchronous 4 bit BCD counter       | 49 |

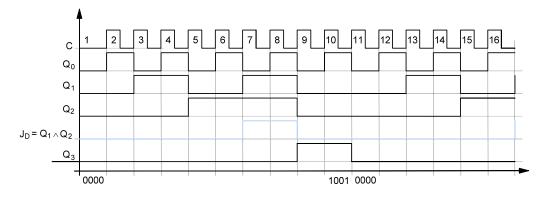

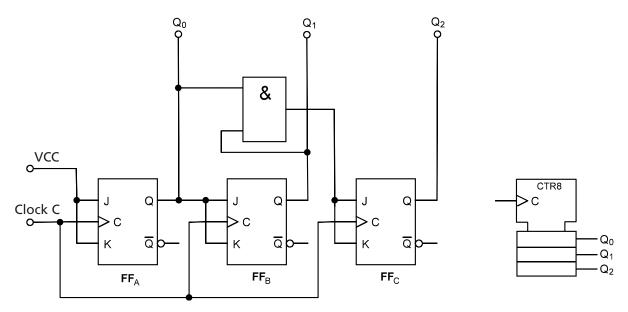

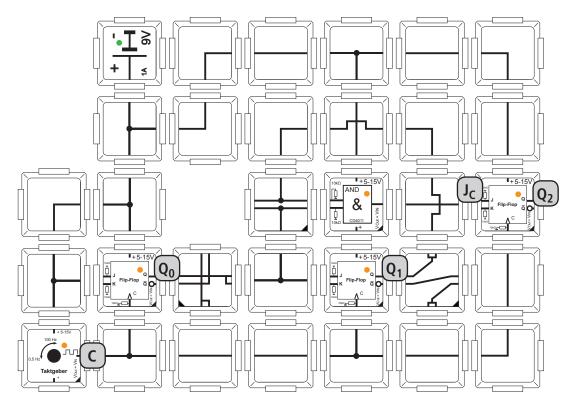

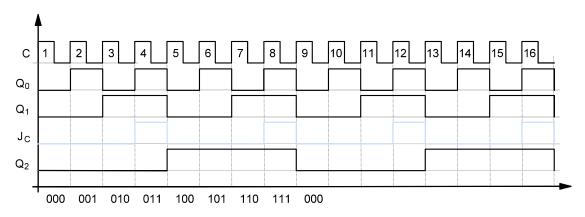

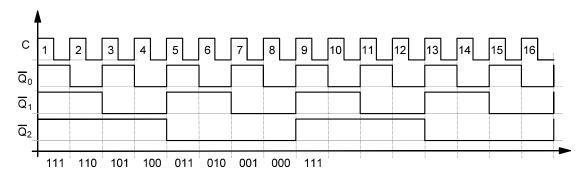

|    | 5.6.3 Synchronous 3 bit binary counter     | 51 |

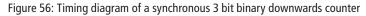

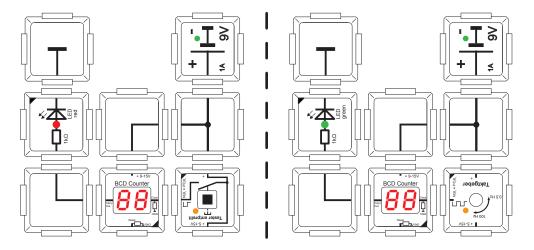

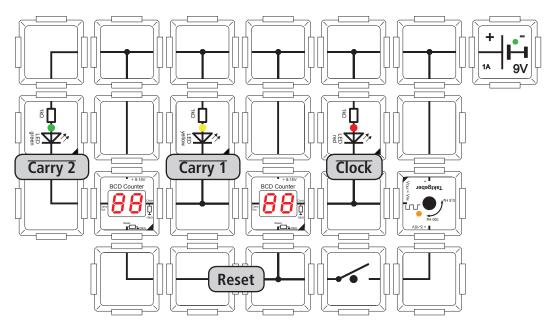

|    | 5.6.4 BCD counter with carry out and reset | 53 |

|    | 5.7 Frequency divider                      | 55 |

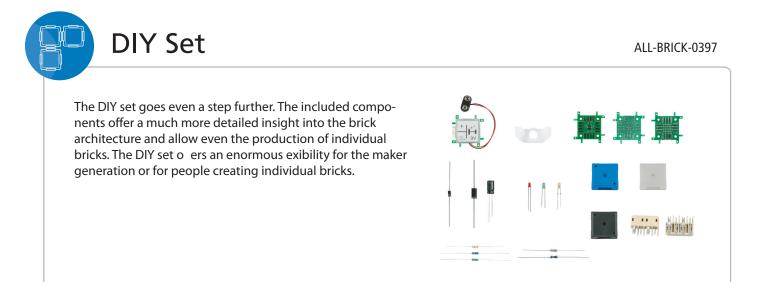

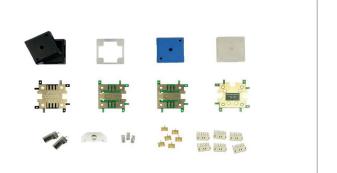

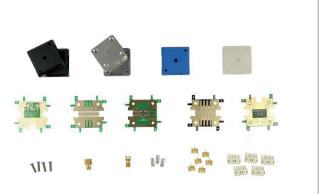

| 6. | Brick community                            | 56 |

| 7. | Overview of the brick sets                 | 59 |

# Preface

The Brick'R'knowledge experimental system has been launched at the HAM Radio faire on the 28th june of 2014 by Rolf-Dieter Klein (ham radio name: DM7RDK). The special thing of our electronic sets is that all of the bricks are connected via a plug system in which all parts are structually identical (hermaphrodite). This way it is possible to also realize tricky circuits. Furthermore you can plug the individual bricks together in different angles. For the return of the ground (0 Volt) there are even two contacts! This way you can build compact circuits in which the ground brick anables a stable voltage supply of the bricks. Another special feature is that you can explain and document these circuits in an easy way.

I wish you lots of fun with the Logic Set

Rolf-Dieter Klein

# List of references:

- Elektronik-Kompendium by Patrick Schnabel: http://www.elektronik-kompendium.de/sites/dig/index.htm

- Elektroniktutor by Detlef Mietke: http://www.elektroniktutor.de/digital1.html

- Wikipedia: https://www.wikipedia.de

You will find comprehensive basic knowledge about digital circuit technology and the laws of Boolean algebra.

# 1. Safety instructions

Note: Never connect the bricks directly to the main power supply (115V/230V). There might be danger to life!

Please only use the included power supply bricks. The voltage of our power supply is 9V, which is not a health hazard. Please

also ensure that no openly wires are in contact with the main power outlets. Otherwise there might be a danger of hazardous electric shocks. Never look straight into LEDs, since this may damage your eye retina. Please remove the power supply brick everytime you finished expimenting, to avoid the risk of an electric fire.

Do not swallow parts of the electronic set. If you did please contact a doctor immediately!

# 2. Basics of the Brick'R'knowledge system

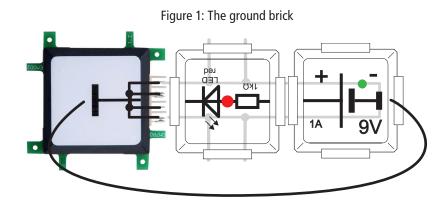

# 2.1 The ground brick

One of the most important bricks is the so called ground brick. The ground brick has one connector with for contacts. Usually the middle two contacts are used for signal or power connection. But the outer contacts are intended for the so called ground level. Which means technically a level of 0V. The ground brick connects the both inner contacts with the outer contacts. Therefore it is possible to allow for a current return flow towards the 0V of a power supply invisible to the schematic symbols outside. The power supply of course must also beconnected at one pole (usually the minus pole) to the ground using the ground brick.

# 2.2 Die Spannungsversorgung

Figure 2: The power supply

The power supply of the Logic Set is achieved by the included 9V power supply brick. The power supply provides a stabilzed directcurrent voltage of 9V and a maximum current of 1A. If overload occurs, the power supply turns off, meaning that it is short-circuitproof.

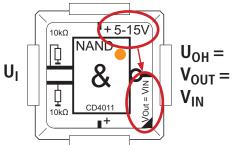

Gates, flip-flops and counter bricks are active components. For those bricks we use the clasical CMOS technology (for details see chapter 4.4) and they need a different power supply. Theoretically you can plug them to any stabilized direct-circuit power source in the range of +5V to +15V. Even though we recommend to use the included power supply brick.

Please always check the circuit before adding the power supply brick. After every experiment, please remove the power supply from the main supply.

Alternatively we offer a battery brick (ALL-BRICK-0001), using a 9V block battery.

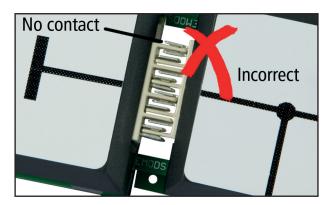

# 2.3 The connectors

Please connect the bricks correctly, otherwise the connection will have an open or short circuit.

Plugged together correctly

Not correctly plugged together

Figure 3: The connectors

The image on the left shows an example of a correctly plugged connection. The connection consists of small contacts, that stuck mechanically and transmit the electrical energy.

The image on the right shows an incorrect connection. As you can see, the metal contacts are interrupted by the plastic pins. This allows no current flow.

Caution: It is important to check the correct connection of the bricks. If they are not connected correctly this can lead to a short circuit or a malfunction of the circuit. If the connection is not working correctly, the current takes the lowest resistance way back to the power source, which might result in a short circuit, because the only resistance that has to be overcome, is the internal resistance of the voltage source.

Important: Always check the correct position of the contacts!

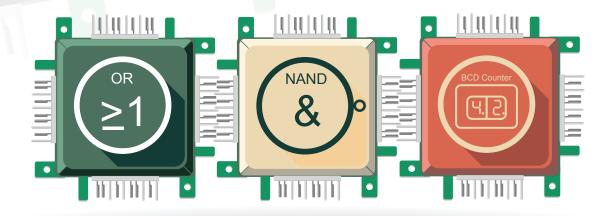

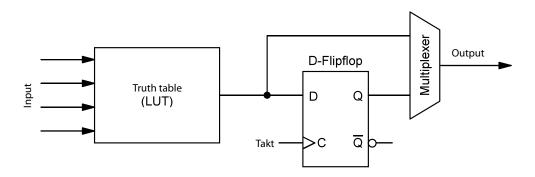

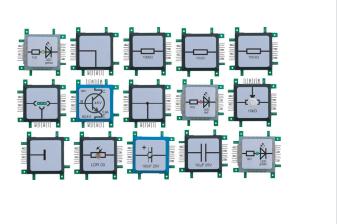

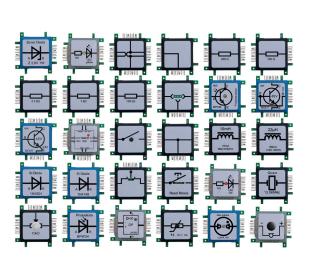

# 3. The Logic Set

The task of the Brick'R'knowledge Logic Set is to teach the basics of the digital circuit technology in an easy and understandable way. This is done on one hand by this detailed, didactical manual and on the other hand by the practice-oriented plugging together and experimenting with the bricks. We start with easy logical linkings to half- and full-adders, to flip-flop- circuits and a BCD counter. As clock we use the famous Timer 555.

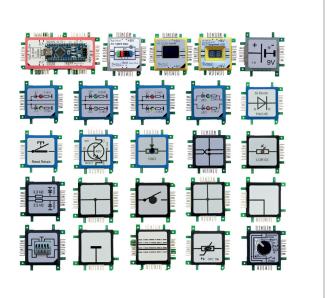

# 3.1 Bricks of the Logic Set

| Scheme                                                                                                                                                               | Qty. | ArtNr. / Brick ID                          | Short description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                      | 1    | ArtNr.: 118627<br>Brick-ID: ALL-BRICK-0221 | <b>9V power supply</b><br>The power supply adapter provides a stabilized<br>DC voltage of 9V with a maximum short-circuit-<br>proof current flow of 1A. The ground is connec-<br>ted to the minus pole, so that no further ground<br>brick must be used on this pole to complete the<br>circuit. A LED signals the correct insertion of the<br>brick. To reduce the risk of electronic malfunc-<br>tions, the power-supply-brick should be discon-<br>nected after an experiment. |

| 10kΩ +5-15V<br>AND<br>B<br>CD4011<br>10kΩ +                                                                                                                          | 2    | ArtNr.: 128276<br>Brick-ID: ALL-BRICK-0437 | <b>AND gate</b><br>This gate realises a logical AND linkage with<br>two inputs based on 1/4 CD4011. The inputs are<br>connected with ground via a $10k\Omega$ pulldown<br>resistor. Supply voltage: +515V.                                                                                                                                                                                                                                                                        |

| $\begin{array}{c c} & & & +5-15V \\ \hline 10k\Omega & & & \\ \hline 0R & & & \\ \hline 21 & & & \\ 10k\Omega & & & \\ \hline 10k\Omega & & & \\ \hline \end{array}$ | 1    | ArtNr.: 128277<br>Brick-ID: ALL-BRICK-0438 | <b>OR gate</b><br>This gate realises a logical OR linkage with two<br>inputs based on 1/4 CD4011. The inputs are<br>connected with ground via a $10k\Omega$ pulldown<br>resistor. Supply voltage: +515V.                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                      | 1    | ArtNr.: 135015<br>Brick-ID: ALL-BRICK-0634 | <b>Inverter</b><br>The inverter negates the signal at the output.<br>The inputs are connected with ground via a<br>10kΩ pulldown resistor. Supply voltage: +515V.                                                                                                                                                                                                                                                                                                                 |

| Scheme | Qty. | ArtNr. / Brick ID                          | Short description                                                                                                                                                                                                                                                                               |

|--------|------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 1    | ArtNr.: 113684<br>Brick-ID: ALL-BRICK-0057 | <b>NAND gate</b><br>This gate realises a logical NAND linkage with<br>two inputs based on 1/4 CD4011. The inputs are<br>connected with ground via a $10k\Omega$ pulldown<br>resistor. Supply voltage: +515V.                                                                                    |

|        | 2    | ArtNr.: 113685<br>Brick-ID: ALL-BRICK-0058 | <b>NOR gate</b><br>This gate realises a logical NOR linkage with<br>two inputs based on 1/4 CD4011. The inputs are<br>connected with ground via a $10k\Omega$ pulldown<br>resistor. Supply voltage: +515V.                                                                                      |

|        | 2    | ArtNr.: 128278<br>Brick-ID: ALL-BRICK-0439 | <b>XOR gate</b><br>This gate realises a logical XOR linkage with<br>two inputs based on 1/4 CD4011. The inputs are<br>connected with ground via a $10k\Omega$ pulldown<br>resistor. Supply voltage: +515V.                                                                                      |

|        | 1    | ArtNr.: 128279<br>Brick-ID: ALL-BRICK-0440 | <b>XNOR gate</b><br>This gate realises a logical XNOR linkage with<br>two inputs based on 1/4 CD4011. The inputs are<br>connected with ground via a $10k\Omega$ pulldown<br>resistor. Supply voltage: +515V.                                                                                    |

|        | 4    | ArtNr.: 113683<br>Brick-ID: ALL-BRICK-0056 | <b>JK flip-flop</b><br>This JK flip-flop (one edge-controlled) is based<br>on the 1/2 CD4027. The JK and clock inputs<br>are connected with ground via a $10k\Omega$ resistor.<br>Supply voltage: +515V.<br>Notice: You should not connect any further load<br>e.g. a LED to the clock input C. |

| Scheme                                                | Qty. | ArtNr. / Brick ID                          | Short description                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------|------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                       | 4    | ArtNr.: 135012<br>Brick-ID: ALL-BRICK-0632 | <b>D</b> flip-flop<br>This is a D flip-flop (edge-controlled). The data<br>and clock inputs are connected with ground<br>via a $10k\Omega$ pulldown resistor. Supply voltage:<br>+515V.<br>Notice: You should not connect any further load<br>e.g. a LED to the clock input C.                                                                                                                                              |

|                                                       | 1    | ArtNr.: 135014<br>Brick-ID: ALL-BRICK-0633 | <b>D flip-flop with set and reset</b><br>This is a D flip-flop (edge-controlled) with a set<br>and reset input in the 2x1 format. All inputs are<br>connected with ground via a 10kΩ pulldown<br>resistor. Supply voltage: +515V.<br>Notice: You should not connect any further load<br>e.g. a LED to the clock input C.                                                                                                    |

| + 9-15V<br>BCD Counter<br>Out<br>Out<br>Reset<br>10kΩ | 2    | ArtNr.: 135011<br>Brick-ID: ALL-BRICK-0631 | <b>BCD counter</b><br>The BCD counter is based on a synchronous<br>counter block CD4518. With this brick it is very<br>easy to build a two-digit BCD counter. The clock<br>and reset inputs are connected with ground via<br>a 10k $\Omega$ pulldown resistor. For cascading several<br>BCD counters, the carry out of the ten's digit is<br>lead through. Clock input and output are low<br>active. Supply voltage: +915V. |

| 0,5 Hz<br>Clock                                       | 1    | ArtNr.: 137826<br>Brick-ID: ALL-BRICK-0643 | <b>Clock</b><br>The clock brick is the clock source for the logic<br>bricks. The circuit is based on the universal timer<br>555. You can change the square wave signal<br>from ca. 0,5 Hz to 100 Hz by turning the poten-<br>tiometer knob. To create single square wave<br>signals you can also use the debounced push<br>button. Voltage supply: +515V.                                                                   |

| Scheme                      | Qty. | ArtNr. / Brick ID                          | Short description                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------|------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| + 5-15V<br>Taster entprellt | 1    | ArtNr.: 137825<br>Brick-ID: ALL-BRICK-0641 | <b>Push button debounced</b><br>With this special push button it is very easy to<br>create a debounced clock signal for flip-flop<br>circuits. Alternatively you can also use the clock<br>brick. By using the debounced push button, the-<br>re is enough time to understand the individual<br>steps of a sequential circuit. The supply voltage<br>is +515V.                                                                                       |

|                             | 3    | ArtNr.: 113644<br>Brick-ID: ALL-BRICK-0017 | <b>Push button</b><br>The push button is an electromechanical switch<br>that allows a conductive connection<br>only during pressing and holding the button. At<br>the moment of release, the connection will open<br>again and the button returns to its inital posi-<br>tion. Note: This push button does not create a<br>debounced signal. By using this brick within logic<br>circuits it can lead to wrong pulses (see chapter<br>5.2, page 33). |

|                             | 1    | ArtNr.: 137824<br>Brick-ID: ALL-BRICK-0642 | <b>Push button dual</b><br>This brick contains 2 push buttons. With this<br>brick it's convenient to control gates or flip-flops.<br>Additionally the two signals are seperated from<br>each other. Connect the supply to the upper or<br>lower connector to save time and wire bricks.                                                                                                                                                              |

|                             | 1    | ArtNr.: 125693<br>Brick-ID: ALL-BRICK-0410 | <b>LED dual grounded, red/yellow &amp; sig-<br/>nal through-connected</b><br>There are two LEDs (red and yellow) in this<br>brick. Additionally there is one series resistor<br>(2.2KOhm) used per piece that protects the<br>LEDs. They are optimated for 2mA. Both of the<br>resistors are grounded. Additionally the signals<br>are transfered to the end.                                                                                        |

|                             | 1    | ArtNr.: 125682<br>Brick-ID: ALL-BRICK-0409 | <b>LED dual grounded, green/orange &amp; signal through-connected</b><br>There are two LEDs (green and orange) in this brick. Additionally there is one series resistor (2.2KOhm) used per piece that protects the LEDs. They are optimated for 2mA. Both of the resistors are grounded. Additionally the signals are transfered to the end.                                                                                                         |

| Scheme           | Qty. | ArtNr. / Brick ID                          | Short description                                                                                                                                                                                                                              |

|------------------|------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | 1    | ArtNr.: 113636<br>Brick-ID: ALL-BRICK-0009 | <b>LED red</b><br>This is a red LED with an included series resistor<br>of $1k\Omega$ . The cathode is displayed by the bar at<br>the LED symbol.                                                                                              |

|                  | 1    | ArtNr.: 113638<br>Brick-ID: ALL-BRICK-0011 | <b>LED yellow</b><br>This is a yellow LED with an included series resistor of $1k\Omega$ . The cathode is displayed by the bar at the LED symbol.                                                                                              |

| 1kΩ LED<br>green | 1    | ArtNr.: 113639<br>Brick-ID: ALL-BRICK-0012 | <b>LED green</b><br>This is a green LED with an included series resistor of $1k\Omega$ . The cathode is displayed by the bar at the LED symbol.                                                                                                |

|                  | 1    | ArtNr.: 113637<br>Brick-ID: ALL-BRICK-0010 | <b>LED blue</b><br>This is a blue LED with an included series resistor<br>of $1k\Omega$ . The cathode is displayed by the bar at<br>the LED symbol.                                                                                            |

|                  | 4    | ArtNr.: 113630<br>Brick-ID: ALL-BRICK-0003 | <b>Wire ground</b><br>The ground is responsible for leading and<br>returning the voltage. Put the ground brick on<br>the end of each circuit in order to close it. It<br>connects the middle connectors with the two<br>external ground lines. |

| Scheme | Qty. | ArtNr. / Brick ID                          | Short description                                                                                                                                        |

|--------|------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 10   | ArtNr.: 113631<br>Brick-ID: ALL-BRICK-0004 | <b>Wire straight</b><br>This straight connector brick connects two<br>opposite bricks.                                                                   |

|        | 8    | ArtNr.: 113632<br>Brick-ID: ALL-BRICK-0005 | <b>Wire corner</b><br>You can connect your brick with the corner brick<br>across the corner.                                                             |

|        | 8    | ArtNr.: 113633<br>Brick-ID: ALL-BRICK-0006 | <b>Wire T-crossing</b><br>With the T-crossing brick you can connect your<br>bricks like with each other like a "T".                                      |

|        | 3    | ArtNr.: 113634<br>Brick-ID: ALL-BRICK-0007 | Wire crossing connected<br>The crossing brick connects all four connectors<br>with each other.                                                           |

|        | 7    | ArtNr.: 113635<br>Brick-ID: ALL-BRICK-0008 | <b>Wire crossing not connected</b><br>This brick connects the opposite connectors. Left<br>to right and up to down without connected the<br>two signals. |

| Scheme | Qty. | ArtNr. / Brick ID                          | Short description                                                                                                                 |

|--------|------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|        | 1    | ArtNr.: 113681<br>Brick-ID: ALL-BRICK-0054 | <b>Wire double corner</b><br>This is a corner brick for two seperated signals.                                                    |

|        | 1    | ArtNr.: 113676<br>Brick-ID: ALL-BRICK-0049 | <b>Wire double straight</b><br>This is a straight connector brick for two sepera-<br>ted signals.                                 |

|        | 2    | ArtNr.: 122443<br>Brick-ID: ALL-BRICK-0381 | <b>Wire T-crossing double left/right</b><br>This is a dual T-crossing left/right which is used<br>to seperate or connect signals. |

|        | 1    | ArtNr.: 113675<br>Brick-ID: ALL-BRICK-0048 | Wire double crossed<br>With this brick you can forward and cross sepe-<br>rated signals.                                          |

|        | 1    | ArtNr.: 113678<br>Brick-ID: ALL-BRICK-0051 | Wire double crossing not connected<br>This brick makes it possible to cross seperated<br>signals without connecting them.         |

| Scheme | Qty. | ArtNr. / Brick ID                          | Short description                                                                                                                                                                                                 |

|--------|------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 4    | ArtNr.: 113679<br>Brick-ID: ALL-BRICK-0052 | Wire double T-crossing left<br>This is a t-crossing left brick for seperated<br>signals. Alternatively we also offer a Wire double<br>t-crossing brick right (article number 113680,<br>brick ID ALL-BRICK-0053). |

|        | 4    | ArtNr.: 122442<br>Brick-ID: ALL-BRICK-0380 | Wire double duplexer left/right<br>This is a duplexer left/right to seperate signals.                                                                                                                             |

|        | 5    | ArtNr.: 113677<br>Brick-ID: ALL-BRICK-0050 | <b>Wire double special</b><br>This is a special wire brick to distribute sepera-<br>ted signals. A typical use for this brick are logic<br>circuits and circuits with controllers e.g. the<br>Arduino brick.      |

# 4. Basics of digital circuitry

# 4.1 What does digital mean?

The term "digital" derives from Latin and means finger. Young children learn how to count and calculate by using their fingers. They serve as an elementary arithmetic unit. We will focus on the binary digital technology that only knows two possible signal states:

- logical zero "0" or "L" (English low) and logical one "1"

- or H (English high)

). In contrast to it there is the term "analogue" (for example analogue vs. digital camera). We can easily explain the difference by comparing a slant with a staircase. While a slant has a continuous change of height a staircase has little discrete steps. Similar to digital information processing that differentiates only between logical zero "0" and "1", in analogue technology signals are processed value-continuously.

The main components of digital circuitries are logic gates like NOT, AND and OR. You can build all kinds of other gates, numerators, flip-flops etc. Complex circuits include storage switching circuits and processors as well as freely programmable logic components.

In case a high voltage level is indicated as "1" and a low voltage level as "0" we speak of positive logic, If a high voltage level is indicated as "0" and a low voltage level "1" we speak of negative logic.

# 4.2 Logical functions

Logical functions (also known as "Boolean functions") are labled as logic gates or simply as gates. There are the three basic logical functions NOT, AND and OR of which consist the functions NAND, NOR, XOR and XNOR. Each logical element can be described by a switch function. Common forms of presentation for this include the Boolean equation and the truth table.

When a digital circuit consists only of logical elements without feedback of output and input, we speak of a clear combinational logic or a combinatorial circuit (compare chapter 4.5, page 21). In addition to logical functions, digital circuits can include storing elements like flip-flops that work synchronously or statefully. As soon as at least one output is directed to the input we speak of sequential circuit or machine (compare 4.6, page 21).

#### **Basic functions**

| Circuit symbol                                              | Designation       | Equation             | Truth table                                             |

|-------------------------------------------------------------|-------------------|----------------------|---------------------------------------------------------|

| Х — 1 — У                                                   | NOT (Negation)    | $y = \overline{x}$   | x         y           0         1           1         0 |

| x <sub>1</sub> &<br>x <sub>2</sub> y                        | AND (Conjunction) | $y = x_1 \wedge x_2$ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$  |

| $\begin{array}{c} x_1 \\ x_2 \\ x_2 \end{array} \ge 1 \\ y$ | OR (Disjunction)  | $y = x_1 \lor x_2$   | $\begin{array}{c c c c c c c c c c c c c c c c c c c $  |

| Composed functions                                                                    |                       |                                                                    |                                                        |  |  |  |

|---------------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------------------|--------------------------------------------------------|--|--|--|

| Circuit symbol                                                                        | Designation           | Equation                                                           | Truth table                                            |  |  |  |

| x <sub>1</sub> &<br>x <sub>2</sub> & y                                                | NAND (Exclusion)      | $y = \overline{x_1 \wedge x_2}$                                    | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |  |  |  |

| $\begin{array}{c} x_1 \\ x_2 \end{array} \ge 1 \\ x_2 \end{array} \xrightarrow{>1} y$ | NOR (Nihilition)      | $y = \overline{x_1 \lor x_2}$                                      | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |  |  |  |

| $x_1 = 1$<br>$x_2 = 1$ $y$                                                            | XOR (Anticoincidence) | $y = (\overline{x_1} \wedge x_2) \lor (x_1 \wedge \overline{x_2})$ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |  |  |  |

| $x_1 = 1$<br>$x_2 = y$                                                                | XNOR (Equivalent)     | $y = (x_1 \wedge x_2) \lor (\overline{x_1} \wedge \overline{x_2})$ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |  |  |  |

Please note: The display of circuit symbols complies with IEC 60617-12.

# 4.3 Comparing number systems

|                 |                            | Binary                     | number                     |                            | Decimal                      | number                      | Hexadecimal number*         |

|-----------------|----------------------------|----------------------------|----------------------------|----------------------------|------------------------------|-----------------------------|-----------------------------|

| Value of digits | <b>8</b> (2 <sup>3</sup> ) | <b>4</b> (2 <sup>2</sup> ) | <b>2</b> (2 <sup>1</sup> ) | <b>1</b> (2 <sup>0</sup> ) | <b>10</b> (10 <sup>1</sup> ) | <b>1</b> (10 <sup>0</sup> ) | <b>1</b> (16 <sup>0</sup> ) |

| Zero            | 0                          | 0                          | 0                          | 0                          | 0                            | 0                           | 0                           |

| One             | 0                          | 0                          | 0                          | 1                          | 0                            | 1                           | 1                           |

| Two             | 0                          | 0                          | 1                          | 0                          | 0                            | 2                           | 2                           |

| Three           | 0                          | 0                          | 1                          | 1                          | 0                            | 3                           | 3                           |

| Four            | 0                          | 1                          | 0                          | 0                          | 0                            | 4                           | 4                           |

| Five            | 0                          | 1                          | 0                          | 1                          | 0                            | 5                           | 5                           |

| Six             | 0                          | 1                          | 1                          | 0                          | 0                            | 6                           | 6                           |

| Seven           | 0                          | 1                          | 1                          | 1                          | 0                            | 7                           | 7                           |

| Eight           | 1                          | 0                          | 0                          | 0                          | 0                            | 8                           | 8                           |

| Nine            | 1                          | 0                          | 0                          | 1                          | 0                            | 9                           | 9                           |

| Ten             | 1                          | 0                          | 1                          | 0                          | 1                            | 0                           | A                           |

| Eleven          | 1                          | 0                          | 1                          | 1                          | 1                            | 1                           | В                           |

| Twelve          | 1                          | 1                          | 0                          | 0                          | 1                            | 2                           | С                           |

| Thirteen        | 1                          | 1                          | 0                          | 1                          | 1                            | 3                           | D                           |

| Fourteen        | 1                          | 1                          | 1                          | 0                          | 1                            | 4                           | E                           |

| Fifteen         | 1                          | 1                          | 1                          | 1                          | 1                            | 5                           | F                           |

The respective number system is indicated by its basis: the basis is lowered in parenthesis, for example 1100(2) = 12(10) = C(16).

In addition to the binary system with the basis 2, the hexadecimal system with the basis 16 is frequently used in digital technology. Binary numbers are relatively long and difficult to overlook. As 16 is a potency of 2, it is especially easy to convert binary numbers into hexadecimal numbers. In this case, four digits of the binary numbers are replaced by one hexadecimal digit – which increases greater clarity. The hexadecimal digits with the value 0-9 are represented by the number symbols 0-9. The values 10-15 are represented by the captial letters A-F - which is why they are clearly readable.

Hence, you can easily determine that ADF5(16) is bigger than ABF1(16) while the respective binary numbers 1010110111110101(2) and 1010101111110001(2) are not as transparent.

The Latin-Greek combination of words in "Hexadecimal" derives from Greek hexa "six" and Latin decem "ten". Also compare: https://en.wikipedia.org/wiki/Hexadecimal

# 4.4 Logic level

Voltage levels are defined to process and display digital signals. Regarding binary coded signals, two voltage ranges are enough that represent the information. These are called High Level (or H Level, High or H) and Low Level (L Level, Low or L).

The High Level, that is the higher voltage, is equivalent to the operating voltage (e.g. 9 V with bricks); the Low Level being the lower voltage is at 0 V (usually called ground). The more or less steep transition from Low to High Level is also called rising or positive edge and the transition from High to Low Level is called falling or negative edge. The change between both levels has to occur with a minimum edge steepness that is usually defined in the manufacturer's data sheet.

Regarding our Logic bricks, the output level complies with the supply voltage that varies between +5V and +15V (exception BCD Counter Brick: 9-15V). When using the provided power supply adapter or a 9V monobloc battery it is 9V. Consequently, the output High Level Uoh corresponds approximately to the supply voltage (as usual in CMOS components).

Output level of the bricks

#### 4.4.1 Voltage ranges

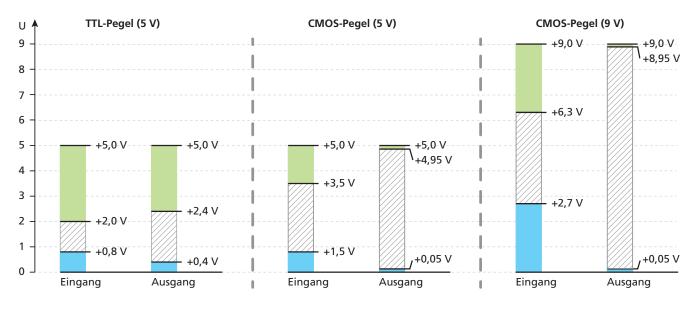

The voltage ranges are prescribed by the different "Logic Families". Logic Families are concidered to be electronic circuits (ICs) that have identical logic levels, temporal behaviours, driver properties, manufacturing processes etc.

To demonstrate both logic values we have relatively huge level ranges (blue and green in the graphic). This makes sense for real logic circuits to recognize the conditions in spite of tolerance. The range between both input level ranges of a logic gate, that is, between UIL and UIH is not permitted (prohibited range), the signal range cannot clearly be assigned to a logic value (hatched graphic). This is why there is a minimum output voltage UOH guaranteed for a High Level range on the output and there is a minimum input voltage UIH requested on the input. The output voltage UOH is always higher than the input voltage UIH. The difference UOH – UIH that ensures the circuits' operational safety is called static interference distance. Low Level ranges have a maximum output voltage UOL, the maximum input voltage UIL and the static interference distance UIL – UOL.

## 4.4.2 Logic states

The level information L and H must not be mixed up with the logic states 0 and 1. L and H indicate the real voltage level. For example 0V (Low) or 5V (High). With these level information we refer to the real electric voltage level of a circuit. When you want to describe the logic functioning of a circuit, the level information have to be assigned to the logic states. We differentiate between positive and negative logic.

#### **Positive logic**

When using positive logic, the logic 0 corresponds to the low level and the logic 1 corresponds to the high level.

#### Negative logic

When using the negative logic, the logic 0 corresponds to the high level while the logic 1 corresponds to the low level.

Indications of low active signals are usually marked with an overscore. Alternatively, asterisks or forward slashes are prefixed or follow the indication. The spelling RESET,

\*RESET and /RESET all indicate that the signal RESET is low active.

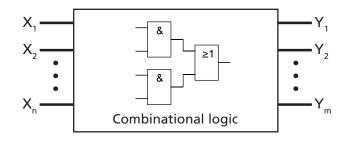

# 4.5 Combinational circuit

The term combinational circuit indicates a combinational circuit that consists of simple basic gates (for example AND, OR, NOT). One or more output variable depend on one or more input variables. There aren't any feedbacks, that means, the gate's output is not reconducted to its input. You could also call this an oblivious act. Signal propagation delays are neglected on the logic leve (compare ch. "Glitches" on p. 22)

Image 6: Combinatorial circuit

## 4.6 Sequential circuit

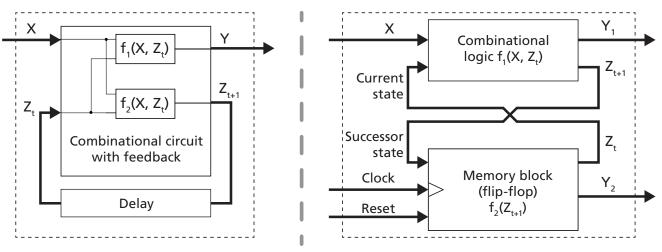

You need circuits with a "memory" in order to solve a problem that does not only depend on a snapshot. This means, you need a circuit that combines input variables at a certain time with values that had occured before that time. Due to the outputs' feedback to the inputs, the circuit gets a storing character. We receive a so called sequential circuit or finite state machine.

Such a sequential circuit consists of a memory block (flip-flop) and a block with combinational logic. The combinational circuit part develops the requested effect Zt+1 and the output variables Y1 out of the current memory block's state and the input variables X.

This part is called Mealy-Automat.

While the output variables Y1 can change in between a state, the outputs Y2 are clocked and free from possible error pulses (so called "Moore Automat").

A sequential circuit is synchronous when the inputs and the feedback are synchronized via clock signals (right image), otherwise they are "asynchronous" (left image).

Image 7: Asynchronous sequential circuit (left) and synchronous sequential circuit (right)

In reality, each combinational circuit generates its outcome only after some time that depends on its development. In order to combine input values with the correct buffered values at a fixed time, the input signals and the feedback outputs are synchronzied via a flip-flop and a clock.

The frequency of the clock signal needs to be big enough for all combinational circuits in the sequential circuit to finish their calculations, this means, for all propagation delays involved to be elapsed.

# 4.7 Glitches

In the field of electronics "glitches" are a short-time false statement in logical circuits and a temporary falsification of a boolean function. This happens since the signal delays of the individual gates are never completly equal. The frequency of glichtes is rising with the complexity and the miniaturization of the circuits and faster clock pulses. Glitches are a significant problem at the development of modern electronical circuits and fast micro processors.

#### Example for the development of glitches:

#### The circuit

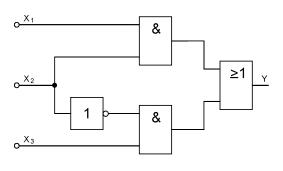

There is a circuit that has three inputs:  $x_3$ . The output is supposed to deploy the value "1" if at least one of the conditions is fulfilled.

- $x_2$  and  $x_1$  are at the same time "1" OR

- x<sub>2</sub> is "0" and x<sub>3</sub> at the same time "1"

If not at least one of the two conditions apply, y should deploy a "0".

#### State 1 - the circuit delivers a 1 as desired

The circuit is now in state 1. According to our specifications, the first condition applies because  $x_2$  and  $x_1$  are "1". The junctions that transmit the information "1

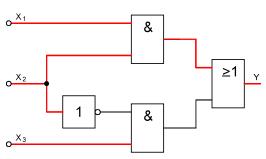

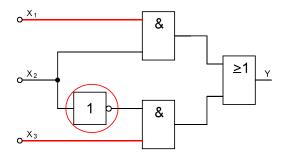

#### State 2 - the inverter causes a glitch

In the state 2,  $x_2 = 0$  and  $x_1 = 1$ . The circuit should still deploy a "1". The inverter needs some time to register the converting of the  $x_2$ -Signals from "0" to "1". For a short time  $x_2 = 0$ , as well as  $\overline{x}_2 = 0$ . The state is is handled as if none of the conditions apply and therefore it deploys a "0". This situation is called "glitch".

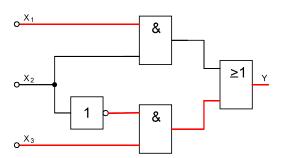

#### State 3 - the circuit delivers the correct value again

After some time - in our case a couple of nanoseconds - the circuit is in state 3: the inverter has processes the new information. The now deployed "1" goes into the AND gate which deploys (again after a few nanoseconds) a "1" as well. Now the OR linkage at y deploys the desired "1".

Figure 8: Development of glitches

In practice, the time difference also exists in gates of the same type and with different lengths. If you want to know the exact values of the function, you have to wait some time until all signals are stable. This fact limits the clock frequency of modern processors significantially.

The impact of glitches in synchronous circuit designs can be prevented through downstream D-Flipflops. The outputs of combinational circuit parts, which consist of diverse logic gates with various terms, need to adapt applicable states just after the clock edge accepts the output values in the D-Flipflops. In the time between two clock edges, any number of glitches can occur through runtime effects in the combinational part, since intermediate states are not noted by the downstream of D-Flipflop.

The method to always equip the outputs of combinational circuit parts with D-Flipflops is one of the essential bases for stable, digital circuit designs in complex all programmable FPGAs (see chapter 4.8.3, page 23)

## 4.8 Programmable logic blocks

Conventional, non-programmable logic bricks have firmly defined functions. These bricks can be bought as integrated circuit (IC), and are also built into the logic bricks. One of the most known logic gates is the NAND gate with type designation 7400 (TTL technology) or 4011 (CMOS technology). By contrast, PLD (programmable logic devices) get their function by appropriate programming of the circuit developer (so called personalization). Some chip manufacturers offer free software tools for circuit designs, implementation (place & route) and simulation.

We created a short overview for the ones who'd like to dip deeper into this topic - especially regarding the FPGA elements: (rising complexity):

## 4.8.1 Programmable Array Logic (PAL) and Generic Array Logic (GAL)

A PAL is a programmable AND array with a fixed OR array. The GAL is in contrast to a PAL rewriteable. The personalization takes place by a programming unit by the circuit developer. In technology, the successor is the CPLD (see next chapter)

## 4.8.2 Complex Programmable Logic Device (CPLD)

A CPLD is made of blocks, which can be connected. The main element is the so called programmable logic arrangement (PLA), that consists of an AND array and an OR array, while both arrays can be programmed. More, an input and output block as well as a programmable feedback exist. Usually, for every I/O pin is a flipflop on hand. This AND/OR matrix allows any combinational link. Due to the structure the throughput times of the CPLD can be - unlike those of the FPGA - defined precisely. Another disparity to the FPGA is the permanent programming by the circuit developer, so the functionality remains even after turning off the supply. The CPLD needn't be refreshed every time the devices is started.

#### 4.8.3 Field Programmable Gate Array (FPGA)

A FPGA consists - similar to the CPLD - of connected, but quit complex blocks. The possibility to connect these blocks is in contrast to the CPLD enlarged. By specific configuration of the intern existing elements, in the FPGA many different circuits and functions can be realised. The range of circuits reaches from less complex projects, like e.g. a simple synchronic meter or decoder, to high complicated circuits, such as memory controller or digital signal processing. Modern FPGA often contain integrated function blocks, like RAM, PLL or whole CPU cores.

FPGA are used in every field of digital technologies, especially in working areas with fast signal processing and high flexibility in changes. So also subsequent changes and improvements in the implemented circuit are possible without causing high costs or time-consuming hardware changes. The high flexibility is perfect for prototypes and for cheap productions of smaller and medium series.

The personalization is carried out "in the field" by the user either by reading the configuration data from an external non-volatile memory such as a PROM (Programmable Read Only Memory) - in this case, the FPGA is "master" or by downloading the data from the computer In the FPGA (slave mode).

After switching on the power supply, the FPGA is initially "dumb". The module is ready for operation only after the so-called configuration phase of a few milliseconds has been completed. FPGAs can be reconfigured at any time in the circuit without a programming device.

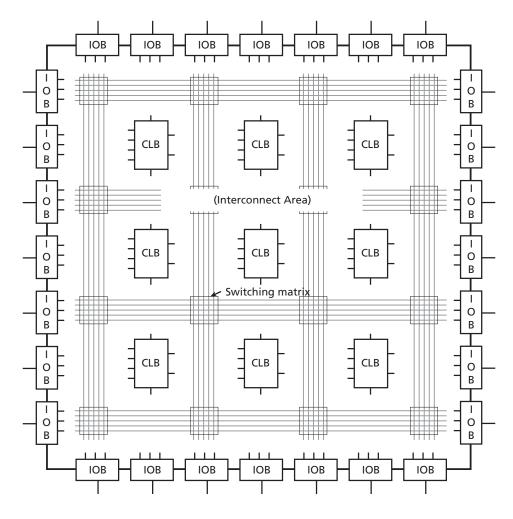

#### 4.8.3.1 Basic structure of FPGAs

The basic structure of FPGAs is a matrix arrangement of configurable logic blocks (CLBs) as well as input / output blocks (IOBs). The latter are usually connected to the pins on the chip. See Fig. 9 on page 24. Between the blocks (CLBs and IOBs) is a lattice of connection paths, also called the interconnect area consisting of a hierarchy of horizontal and vertical "Lines". The inputs and outputs of the blocks are connected to these lines. Remote connections are "wired" through programmable connection points in the switch matrices of the grid. In this way, signal routing (also called routing) is possible over the entire chip.

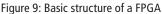

#### 4.8.3.2 Configurable logic blocks

The basic structure of an FPGA is an array of configurable blocks with a programmable truth table (LUT) and a 1-bit register (D-flip-flop). Depending on the number of available inputs, the LUT can implement any n-digit binary function. Common are LUT structures with four binary inputs and more. In addition to the LUTs, multiplexers in the base blocks allow very fast local signal paths, for example for the integration or bypassing of the flip-flop, for feedback of its output, for connecting neighboring blocks and the like.

Figure 10: Logic block example

#### 4.8.3.3 Input / output blocks

The input / output blocks (IOBs) form the interface to the outside world. The FPGA's connections are connected to the switching matrix. Depending on the application, the voltage level of the inputs and outputs can be adapted to the respective interface standard (TTL, LVDS, etc.). In addition, the drive current of the outputs and the edge slope of the output signals, as well as Tristate buffers (pins that can be switched to high impedance) can be activated to set up a bus architecture.

# 5. Circuit examples

# 5.1 Basic circuits

#### 5.1.1 Inverter

The inverter brick realises a NOT function and is therefore also called neation or inverting. This means that the input signal is inverted. If the input of the inverter brick receives a high level, you receive a low level at the output and the other way around.

In our brick circuit we connected a push button and the power supply to the input of the inverter brick. The inverter brick has a built-in pull-down resistor so that it knows what to do if the push button is not pressed.

By pushing the button, there is high level at the input. Therefore the output is low and the LED switches off.

#### Figure 11: Inverter as brick circuit

| Circuit symbol | Description    | Equation           | Truth table                                             |

|----------------|----------------|--------------------|---------------------------------------------------------|

| Х — _ 1 — У    | NOT (Negation) | $y = \overline{x}$ | x         y           0         1           1         0 |

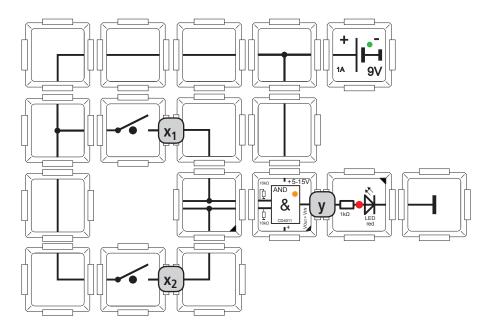

## 5.1.2 AND gate

The AND gate realises a logical AND linkage of two or more inputs. Compared to the NAND gate, the ouput is not inverted.

In our example, the two inputs of the AND gates are connected with the supply voltage via push buttons. As long as no button is pressed, both of the inputs are connected to ground (low level) via the pulldown resistors. This means in the case of an AND linkage that the ouput deploys a defined level. The LED only starts to light up if both push buttons are pressed and the output changes (as you can see in the truth table) to a high level.

Figure 12: AND gate as brick circuit

| Circuit symbol   | Description   | Equation             | Truth tab           | le                  |        |

|------------------|---------------|----------------------|---------------------|---------------------|--------|

| x1 — &           |               |                      | x <sub>1</sub><br>0 | x <sub>2</sub><br>0 | у<br>О |

| x <sub>2</sub> y | (Conjunction) | $y = x_1 \wedge x_2$ | 0                   | 1<br>0              | 0      |

|                  |               |                      | 1                   | 1                   | 1      |

You can also build a AND circuit with two push buttons that are connect in series. Only if you push both buttons  $(x_1 \text{ und } x_2)$  are pressed, the LED (y) lights up. Try this fuction with the help of the truth table above.

Figure 13: Alternative AND circuit with push button

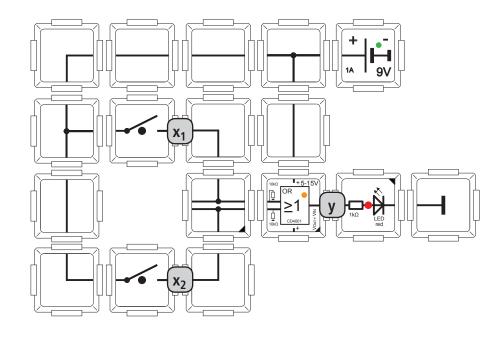

### 5.1.3 OR gate

The OR gate realises a logical OR linkage with two or more inputs. Compared to the NOR gate, the outputs are not inverted.

In our example, the two inputs of the OR gates are connected with the supply voltage via push buttons. As long as no button is pressed, both of the inputs are connected to ground (low level) via the pulldown resistors. This means in the case of an OR linkage that the ouput deploys a defined level. The LED only starts to light up at least one push button is pressed and the output changes (as you can see in the truth table) to a high level.

Figure 14: OR gate as brick circuit

| Circuit symbol      | Description      | Equation           | Truth table                   |   |

|---------------------|------------------|--------------------|-------------------------------|---|

|                     |                  |                    | x <sub>1</sub> x <sub>2</sub> | у |

| X <sub>1</sub> ≥1 y | OR (Disjunction) | $y = x_1 \lor x_2$ | 0 0<br>0 1                    | 1 |

| x <sub>2</sub>      |                  |                    | 1 0                           | 1 |

|                     |                  |                    | 1 1                           | 1 |

An OR circuit can also be built with two push buttons that are connected in parallel. As soon as you press at least one button  $(x_1 \text{ or } x_2)$  the LED (y) lights up. Try this funcationality with the help of the truth table above.

Figure 15: Alternative OR circuit with push button

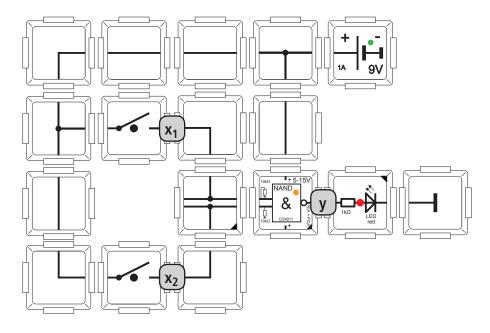

#### 5.1.4 NAND gate

The NAND gate realises a logical AND linkage of two or more inputs with an inverted output. Besides the NOR gate, the NAND gate is the most common type. There is no function that can not be built with these to gates! This shows why those two types are so common in practice.

In our example, the two inputs of the NAND gate are connected with the supply voltage via push buttons. As long as no button is pressed, both of the inputs are connected to ground (low level) via the pulldown resistors. The LED light sup because the inverted output deploys a high level. The LED only switches off if both of the push button are pressed and the output changes (as you can see in the truth table) to a low level.

Figure 16: NAND gate as brick circuit

| Circuit symbol                         | Description      | Equation                        | Truth table                                            |  |

|----------------------------------------|------------------|---------------------------------|--------------------------------------------------------|--|

| x <sub>1</sub> &<br>x <sub>2</sub> > y | NAND (Exclusion) | $y = \overline{x_1 \wedge x_2}$ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |  |

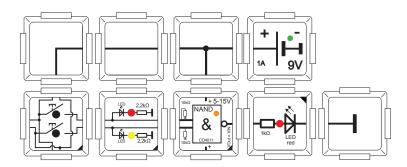

Alternatively you can also build the XOR circuit in a more compact way - the functionality is the same:

Figure 17: Alternative NAND circuit

## 5.1.5 NOR gates

The NOR gate realises a logical OR linkage of two or more inputs with inverted output.

In our example, the two inputs of the NOR gate are connected with the supply voltage via push buttons. As long as no button is pressed, both of the inputs are connected to ground (low level) via the pulldown resistors. The LED lights up because the inverted output deploys a high level. As long as at least one of the two buttons is pressed, the output changes to low level and the LED switches off.

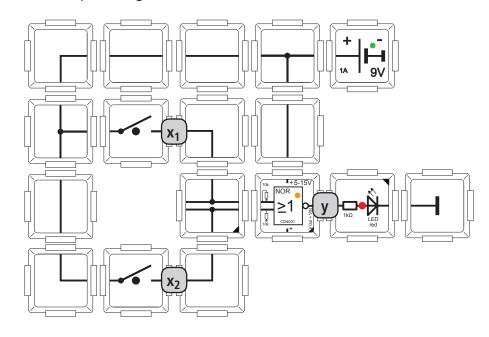

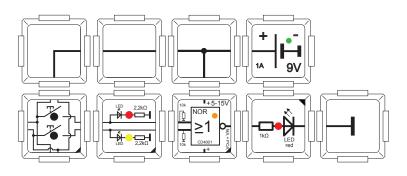

Figure 18: NOR gate as brick circuit

| Circuit symbol                                           | Description      | Equation                      | Truth table    |                  |

|----------------------------------------------------------|------------------|-------------------------------|----------------|------------------|

|                                                          |                  |                               | x <sub>1</sub> | x <sub>2</sub> y |

| $\begin{array}{c} x_1 \\ x_2 \end{array} \ge 1 \qquad y$ | NOR (Nihilition) | $y = \overline{x_1 \vee x_2}$ | 0              | <u>1</u> 0       |

| ^2                                                       |                  |                               | 1              | 0 0              |

|                                                          |                  |                               | 1              | 1 0              |

Alternatively you can also build the XOR circuit in a more compact way - the functionality is the same:

Figure 19: Alternative NOR circuit

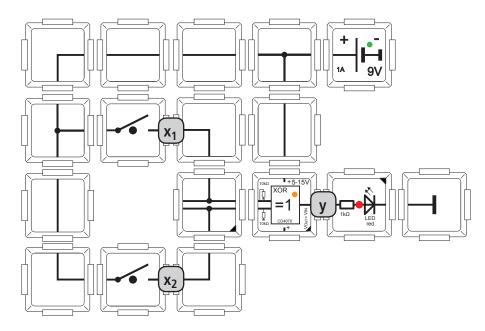

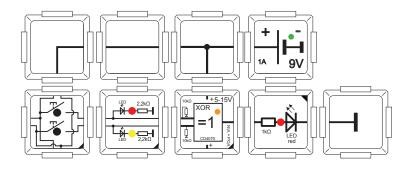

### 5.1.6 XOR gate

The XOR gate is very common in the electronical field. It realises a logical exclusive-or connection with two or more inputs. An easy example is a common toggle switch e.g. the hall light at home. Each switch can be used to switch the light on or off. It doesn't matter which switch you use first. In everyday conversation you would proabably refer to the XOR gate as "either...or". The XOR linkage is an important part of the adder, that we will get to know in chapter 5.3 "digital counter".

In this example, the two inputs of the XOR gate are connected with the supply voltage via push buttons. As long as no button is pushed, both of the inputs are connected to ground (low level) via the two integrated pulldown resistors. The LED does not light up because the output issues a low level. Once "either" button 1 "or" button 2 is pressed, the output is changing to high level and the LED lights up. If no or both buttons are pressed the output changes bach to low level referred to the truth table.

Figure 20: XOR gate as brick circuit

| Circuit symbol | Decription        | Equation                                                         | Truth tab      | ole            |   |

|----------------|-------------------|------------------------------------------------------------------|----------------|----------------|---|

|                |                   |                                                                  | x <sub>1</sub> | x <sub>2</sub> | У |

| X11            |                   |                                                                  | 0              | 0              | 0 |

| $x_2 = 1$ y    | XOR (Antivalence) | $y = (\overline{x_1} \land x_2) \lor (x_1 \land \overline{x_2})$ | 0              | 1              | 1 |

| ^2             |                   |                                                                  | 1              | 0              | 1 |

|                |                   |                                                                  | 1              | 1              | 0 |

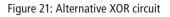

Alternatively you can also build the XOR circuit in a more compact way - the functionality is the same:

## 5.1.7 XNOR gates

The XNOR gate realises logical exclusive-or linkage of two or more inputs. Besides the NAND or NOR gates it is a gate with inverting output. The inverting exclusive-or linkage signalises the equality of the inputs. This can be used for a comparison of different bit patterns. In the case of a bit pattern equality (both inputs "0" or both inputs "1") an interruption signal can be sent to the computer or an acustical or opticalal alarm can be activated.

In our example both of the inputs of the XNOR gate are connected via a button with the supply voltage. As long as no button is pressed, both of the inputs are connected to ground (low level) via the pulldown resistors. This means in the case of a XNOR linkage that the ouput issues a high level. Our red "alarm" LED lights up. The same applies when both of the buttons are pressed at the same time. As soon as only one button is pushed, the output changes back to low level and the LED turns off.

Figure 22: XNOR gate as brick circuit

| Circuit symbol  | Description        | Equation                                                         | Truth tab      | le             |   |

|-----------------|--------------------|------------------------------------------------------------------|----------------|----------------|---|

|                 |                    |                                                                  | x <sub>1</sub> | x <sub>2</sub> | У |

|                 |                    |                                                                  | 0              | 0              | 1 |

| $x_1 = 1$ $p_y$ | XNOR (Equivalence) | $y = (x_1 \land x_2) \lor (\overline{x_1} \land \overline{x_2})$ | 0              | 1              | 0 |

| ^2              |                    |                                                                  | 1              | 0              | 0 |

|                 |                    |                                                                  | 1              | 1              | 1 |

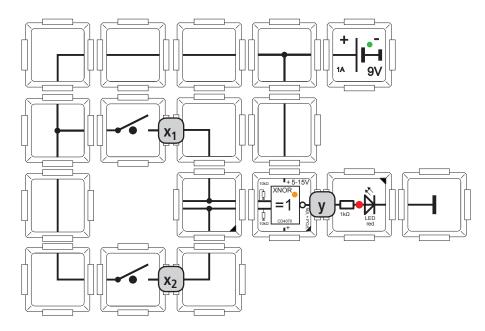

Alternatively you can also build the XNOR circuit in a more compact way - the functionality is the same:

# 5.2 Debounced circuit

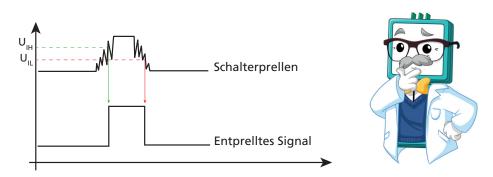

Push buttons and switches have the disadvantage that the operation of the mechanical contact (a spring is often used) causes multiple opening or closing. In the digital technology we call this desruptive effect "chatter" or "bouncing".

Figure 24: Typical intererence pulse because of contact bounce

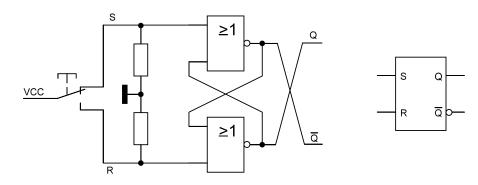

But there is an easy solution for this problem by using a normal RS flip-flop. Basically a RS flip-flop can be built optionally with two NOR or NAND gates. Here we use the version with NOR gates because the NOR bricks already include a pull-down resistor at the inputs. Because of the fast switching speed of the RS flipflop, at first contact it rests stable in this state and saves the logical value until the inputs are wired differently. Because of the pull-down resistors, the blank inputs always have a stable state.

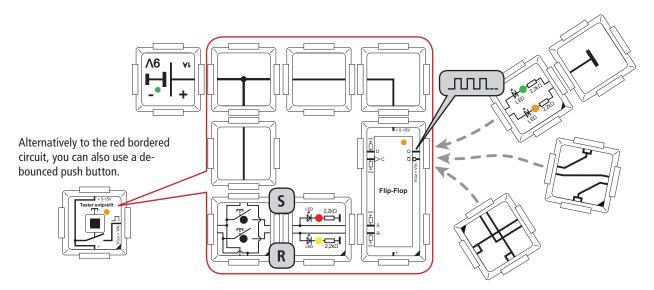

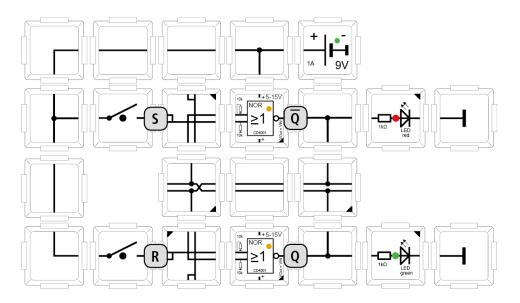

Figure 25: Debounced circuit built with NOR gates (left) and RS flip-flop (right)

Press the push buttons S and R by turns to get a debounced clock pulse at the outputs Q. You can use a clock for this experiment as well.

Figure 26: Debounced circuit with RS flio-flop brick (bordered red) or with debounced push button (left)

# 5.3 Digital counter

By using the already knows logic gates you can build digital circuits to operate arithmetic operations in the binary number system. This digital counter is also knows as ALU (arithmetic logic unit). It is able to connect two inputs with fundamental, arithmetic and logical operations. If you combine an ALU with a control unit (condition follower) and a result register, you receive a so called central processing unit, known as CPU. This means that the heart of every CPU is a ALU and then again the heart of every ALU is a adder. In the simplest case, two single-digit binary number A and B can be added. In the first step we will build a 1-bit half-adder, that we will extend to a full-adder in the second step.

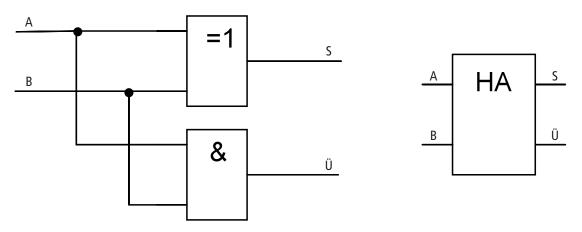

#### 5.3.1 1-bit half-adder

The 1-bit half-adder (HA) is the easiest counter circuit and can add two single-digit numbers with each other. The input A is added to the input B. The sum S is generated with the XOR linkage and the carry out (Ü) with a AND linkage. In principle this is the same way of adding as with the written addition in the decimal number system. Remember: If you reach 10, the next higher digit is noted as a carry out.

The two push buttons represent the summands A and B that should be added. By pressing one of the buttons, you receive the binary value "1": the red sum LED at the output of the XOR gate light up (1+0=1). As soon as both of the push buttons are pressed, meaning that we count 1+1, the sum is "0" and the carry out is "1" (the green LED lights up).

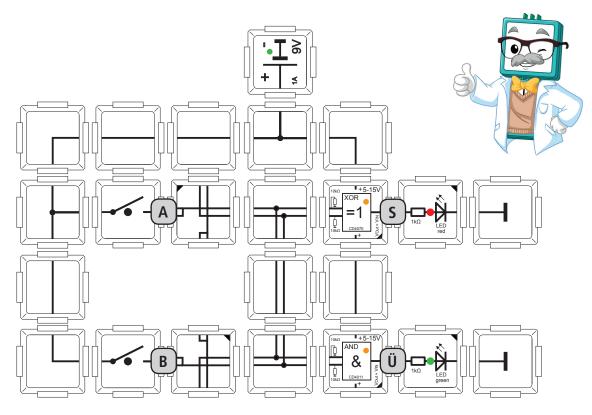

Figure 27: Circuit of a half-adder (left) and its block diagram (right)

#### Truth table of a 1-bit half-adder

| Summand A | Summand B | Sum S | Carry over Ü |

|-----------|-----------|-------|--------------|

| 0         | 0         | 0     | 0            |

| 0         | 1         | 1     | 0            |

| 1         | 0         | 1     | 0            |

| 1         | 1         | 0     | 1            |

Figure 28: 1-bit half-adder as brick circuit

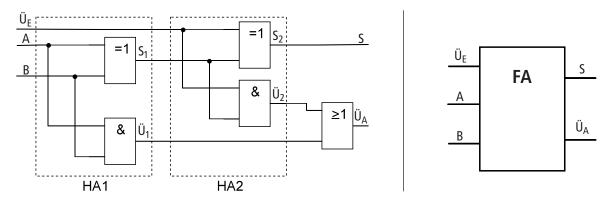

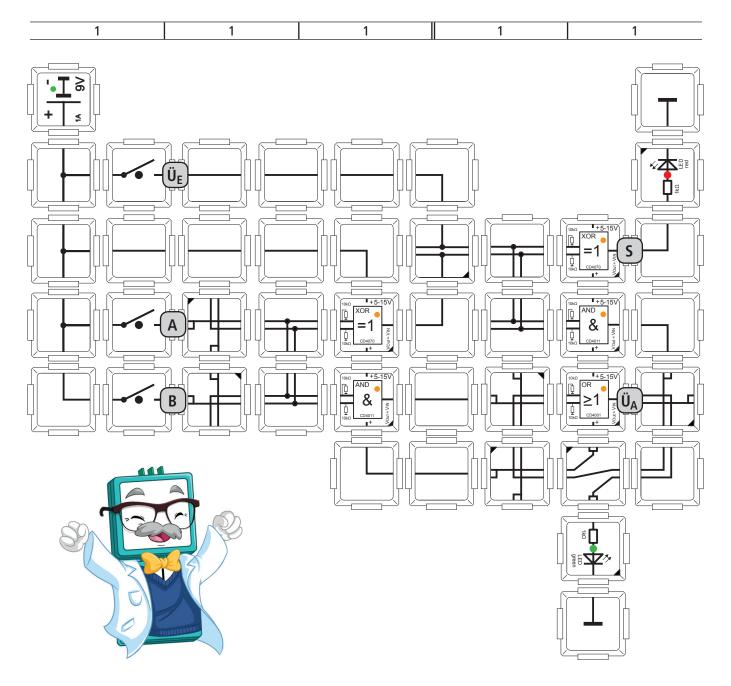

## 5.3.2 1-bit full-adder

If you want to add muti-digit binary numbers, the carry out of each lower digital has to be included into the sum S. We call this additional summand "carry out input".  $\ddot{U}_E$ . Schaltungstechnisch kombinieren wir zwei Halbaddierer (HA) zu einem sog. Volladdierer (VA). Damit können wir zu den beiden Summanden A und B zusätzlich den Übertrag  $\ddot{U}_E$  addieren. Das Ergebnis wird als Summe S (rote LED) und als Übertragsausgang  $U_A$  (grüne LED) angezeigt.

Figure 29: Circuit of a full-adder (left) and block diagram

#### Truth table for a 1-bit full-adder

| Carry out input Ü <sub>E</sub> | Summand A | Summand B | Sum S | Carry out output Ü <sub>A</sub> |

|--------------------------------|-----------|-----------|-------|---------------------------------|

| 0                              | 0         | 0         | 0     | 0                               |

| 0                              | 1         | 0         | 1     | 0                               |

| 0                              | 0         | 1         | 1     | 0                               |

| 0                              | 1         | 1         | 0     | 1                               |

| 1                              | 0         | 0         | 1     | 0                               |

| 1                              | 1         | 0         | 0     | 1                               |

| 1                              | 0         | 1         | 0     | 1                               |

Figure 30: 1-bit full-adder as brick circuit

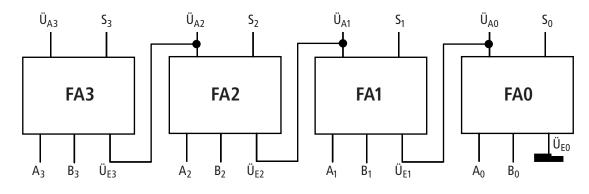

#### 5.3.3 4-bit full-adder

The following block diagram shows a 4-bit full-adder (VA0 to VA3), that is built with four 1-bit full-adders.

Der Eingang Ü<sub>E0</sub> kann mit Masse verbunden werden, da für die niederwertigste Stelle kein Übertrag berücksichtigt werden muss. Die Überträge von VA0 bis VA3 werden jeweils durch die Verbindung der Übertragausgänge Ü<sub>An</sub> mit den Übertragseingängen des jeweils höherwertigeren Addierers Ü<sub>En+1</sub> weitergereicht. Ü<sub>A3</sub> wird hier nicht weiter verwendet.

Figure 31: Block diagram of a 4-bit full-adder

By the way: In the field of digital technology it is common to start the indices for bus connections or logical units with "0". The background ist also that the valence of the digits is displayed as power of two in the binary system: 2n - starting with n = 0. Here is an example:

| $2^{3} = 8$ $2^{2} = 4$ $2^{1} = 2$ $2^{0} = 1$ |

|-------------------------------------------------|

|-------------------------------------------------|

Due to the complexity of the circuit, it is not possible to build the 4-bit full-adder with the bricks of the logic set.

#### 5.4 Flip-flops

Suppose you are waiting for a message but currently you are not at home. Thanks to the letterbox this is no problem because the postman can simply post the letter into it. This way, the message doesn't get lost and you can simply get the mail from the mailbox and read it when you have time. You could also call the postbox a "buffer". The red flag shows you if the postbox contains a message or not. You can imagine a flip-flop, which is the smallest digital storage element, in a simular way to this postbox.

The term "flip-flop" indicates in the digital technology an electronical circuit that can have two stable electrical states (0 and 1). By changing the input signals, the flip-flop can change its state from one to the other.

Therefore we have the possibility to store a digital information (1 bit), as long as there is a supply voltage. The flip-flop is the heart of sequential circuits and is used in various types. In micro processors, several flip-flops are connected in parallel. The width of a register shows us how many flip-flops are connected in parallel in the register. Common units are: 8 bit = 1 byte; 16 bits = 1 word; 32 bits = 1 Longword.

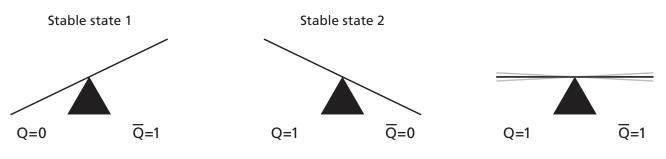

Often the RS flip-flop is also compared to a mechanical rocker:

A rocker has two stable states: Either its left end or its right end toches the floor. By using the appropriate physical effort, you can change its state. In a flip-flop that happens if you active the inputs, R = 0, S = 1 or R = 1, S = 1. If you don't use any physical effort to change the state of the rocker, it rests in the last state: the state is therefore stored. If the rocker is in a horizontal orientation, it has a metastable state (R = 1 and S = 1): In practice, the rocker can never rest in this position. At some point it will change to one or the other side. You can't even tell into which state it changes because you never know all of the exact interferences. A clocked flip-flop is equivalent to the rocker, but the physical effort can only work at a time, that is determined by an external clock signal.

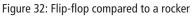

#### 5.4.1 Types of flip-flops

Various flip-flops differ in terms of input amount and its behaviour. They have differently working inputs and only work in specifically defined conditions. An easy flip-flop only has to inputs and two outputs. Clocked flip-flops have an additonal clock input.

Abb. 1: Flipflop-Typen

#### 5.4.1.1 Not clocked flip-flops

Flip-flops without a clock input are completey independet of a clock. Its set and reset inputs (S

and R) are always adressable. See also chapter 5.4.2 on page 40.

#### 5.4.1.2 One-edge-triggered flip-flops

| 1S | Lı       |

|----|----------|

|    |          |

| C1 | i        |

| 1R | <u>ب</u> |

In the one-edge-triggered flip-flop the set and reset inputs are only adressable if the clock signal at the clock input C1 changes its state. This change is displayed by the triangle on the graphic

symbol. See also chapter 5.4.3 on page 41.

#### 5.4.1.3 Einflankengesteuerte Flipflops

Beim einflankengesteuerten Flipflop ist der Setz- und Rücksetzeingang (1S und 1R) nur bei Änderung der Flanke am Takteingang C1 wirksam. Die Störanfälligkeit wird heruntergesetzt. Die Takt flankensteuerung wird im Schaltzeichen durch das Dreieck gekennzeichnet. Siehe auch Kap. 5.4.3 auf Seite 41.

#### 5.4.1.4 Two-edge-triggered flip-flops

The two-edge-triggered registers the input states at the first change of the clock signal and issues the signal at the second change of the clock signal. The change of the clock signal is also called clock edge. This way, the susceptibility is minimized. The clock edge-triggering is displayed by the triangle on the graphic symbol. See more in chapter 5.4.4 on page 42.

Flip-flops whose input signals appear delayed in time at the output, are also called Master-Slave-flip-flops. This is displayed by the rectangular corners at the output. A well-known example for this type of flip-flop is the so called JK-Master-Slave-flip-flop.

In the following chapters you will get to know the flip-flops that are included in the Brick'R'knowledge Logic Set.

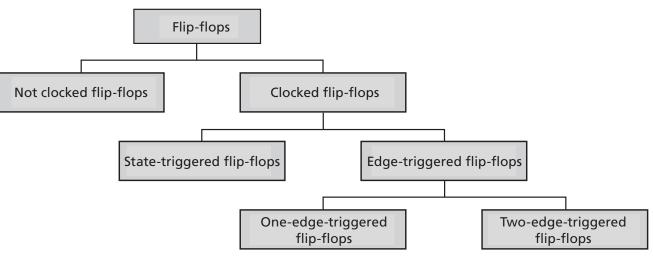

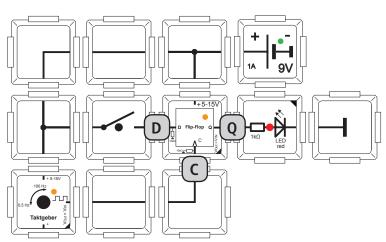

#### 5.4.2 RS flip-flop

The RS flip-flop is an easy not clock-triggered flip-flop that can be built with two NOR gates. This circuit is also called "NOR flip-flop". In principle, this circuit can also be built with two NAND flip-flops, but this would need negated inputs.

Figure 34: Flip-flop built with two NOR gates (left) and the circuit symbol of the RS flip-flop (right)

In the cicuit symbol of the RS flip-flops, the inputs are called S (set) and R (reset). Q is negated to Q. Please consider that the outputs Q and  $\overline{Q}$  are crossed!

#### Truthtable of not edge-triggered RS flip-flops

| Set input S | Reset output R | Output Q | Output Q | Discription      |

|-------------|----------------|----------|----------|------------------|

| 1           | 0              | 1        | 0        | Set (SET)        |

| 0           | 0              | Q        | Q        | No change        |

| 0           | 1              | 0        | 1        | Reset (RESET)    |

| 1           | 1              | 0        | 0        | Prohibited state |

Beachte, dass sich in der folgenden Brick-Schaltung Ausgang Q unten und Ausgang  $\overline{Q}$  is above!

- Set: By pressing the push button at the S input, the output Q is set to "1".

- No change: As long as no push button is pressed, the outputs don't change.

- Reset: By pressing the push button at the R input, the output Q is set to "0".

- Prohibited

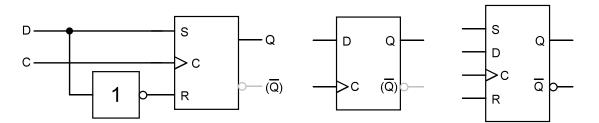

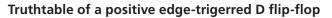

#### 5.4.3 D flip-flop

The D flip-flop consists of a RS flip-flop, whereby the reset input is connected with the set input via an inverter. This prevents the occurrence of the undefined, metastable state.

The D flip-flop is available as state-trigerred and edge-triggered flip-flop, as in this Logic Set. If a D flip-flop also containes RS inputs, it is also possible two set and reset it clock-independtly (asynchronous). See also in chapter 5.2 on page 33).

The D flip-flop is the basic element of the read-only memory. In practice, many D flip-flops are usually connected in parallel and synchronized via a common clock. Such an arrangement of mostly 4, 8, 16 or 32 D flipflops is called a register. A practical application is, for example, a status register which is to be read in order to receive information about a device or a command register to transmit commands to a device. The only input is called a data input. In our case, the value at the data input ("0" or "1") with the positive edge at the clock input C is accepted.